# Timing analysis of an SDL subset in UPPAAL

#### Anders Hessel

April 16, 2002

#### Abstract

SDL is intended for the specification of complex, event-driven, real-time, and interactive applications involving many concurrent activities that communicate using discrete signals.

Although the behaviour of an SDL system is clearly defined by the semantics of SDL, analysis of the real-time behaviour is still hard to do for such a system. Timing and the arrival order of signals is of paramount significance for correct behaviour. So, it would be very difficult to do an exhaustive testing on an SDL system during run-time. This is partially because we cannot control the order of arrival of signals to a process, at least not for signals internal to the SDL system. No matter how many times we run a test suite, it is possible that signals always come in the same order at a specific state of the system.

Happily, there are verification tools for analysis of models of real-time systems e.g., UPPAAL. The basis of the UPPAAL model is the notion of timed automata developed by Alur and Dill as an extension of classical finite—state automata with clock variables. If we could transform an SDL system into a network of timed automata while conserving its behaviour we would be able to let UPPAAL do the verification.

In this report we describe and implement a translation from an SDL (Specification and Description Language) syntax to a language (xta) used in the UPPAAL tool. We show how it is possible to simulate implicit and explicit channels, queues, timers, dynamic process creation and process execution. Apart from timers we can also simulate worst and best execution time per action statement in the process.

## Acknowledgements

This master thesis projects started at ISD Datasystem AB [ISD] in March 1998. I want to thank ISD and its CEO Sven-Eric Berg for this opportunity. I also want to thank, as my supervisor at ISD, Jörgen Carlsson, for discussions on SDL sematics.

After ten weeks, sponsored by ISD, the work continued at my spare time. Around year 2000 a new UPPAAL format was developed by the UPPAAL team, namely the .xta format. This made it possible for me to express my translation output in templates. The project was now expanded to include type based processes and type based blocks.

In the SDL task there was first possible to express "target code" where the target code wasn't parsed at all. Now, with the new .xta I wanted to build a more controlled conversation and decided to fully parse all "target code" that also included some type checking. During this period I had professor Wang Yi as my supervisor, accompanied by the UPPAAL group at Uppsala University. I like to specifically thank Paul Petterson, Wang Yi, Johan Bengtsson, and Fredrik Larsson for this time.

At late September 2001, professor Bengt Jonsson at Uppsala University became my supervisor and sponsor for the last coding and the writing of this report. I own him a lot of thanks for helping me with the report, both structurally and grammatically.

At last, I like to thank Madeleine for her patients during the years.

Anders Hessel, April 2002

# Contents

| A | Acknowledgements |                                               |                  |  |

|---|------------------|-----------------------------------------------|------------------|--|

| 1 | Intr             | oduction                                      | 7                |  |

|   | 1.1              | Overview and objectives                       | 7                |  |

|   | 1.2              | Conversion problems                           | 7                |  |

|   | 1.3              | Organization                                  | 8                |  |

| 2 | SDI              |                                               | 10               |  |

|   | 2.1              | Definition                                    | 10               |  |

|   | 2.2              | History                                       | 10               |  |

|   | 2.3              | Behaviour overview                            | 10               |  |

|   | 2.4              | Structure                                     | 12               |  |

|   | 2.5              | Communication                                 | 14               |  |

|   | 2.6              |                                               | 14               |  |

|   | 2.7              | , <u>, , , , , , , , , , , , , , , , , , </u> | 15               |  |

|   | 2.8              | <u>-</u>                                      | 15               |  |

|   | 2.9              |                                               | 17               |  |

|   | 2.10             |                                               | 17               |  |

|   |                  |                                               | 19               |  |

|   | 2.12             | Timers                                        | 20               |  |

|   |                  |                                               | $\frac{1}{20}$   |  |

| 3 | Upp.             | AAL                                           | 21               |  |

|   | 3.1              |                                               | 21               |  |

|   | 3.2              | <b>U</b>                                      | 21               |  |

|   | 3.3              |                                               | 21               |  |

|   | 3.4              | 6                                             | $\frac{-}{23}$   |  |

|   | 3.5              |                                               | $\frac{25}{25}$  |  |

| 4 | SDI              | run-time system building                      | 27               |  |

| - | 4.1              | · <b>y</b> - · · ·                            | <b>-</b> .<br>27 |  |

|   | 4.2              |                                               | 32               |  |

|   | 4.3              | 0 v                                           | 36               |  |

|   | 4.4              | U I                                           | 42               |  |

| 5 | Pro              | cess conversion                               | 43               |  |

| U | 5.1              |                                               | 43               |  |

|   | 5.1 - 5.2        |                                               | $\frac{43}{43}$  |  |

|   | 5.2              |                                               | 44               |  |

|   | 5.4              | , <u>i</u>                                    | 47               |  |

|   | 5.4              |                                               | 48               |  |

|   | 5.6              |                                               | 40<br>49         |  |

|   |                  | •                                             |                  |  |

|   | 5.7              | Label                                         | 49               |  |

|     | 6.8 Output                                                                                     |

|-----|------------------------------------------------------------------------------------------------|

| •   | $6.9  \mathrm{Task}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ |

|     | 5.10 Create and stop                                                                           |

|     | 5.11 Decision                                                                                  |

|     | 5.12 Set/reset of timers                                                                       |

|     | 5.13 Nextstate                                                                                 |

| 5   | 5.14 Join                                                                                      |

| E   | Brief example                                                                                  |

|     | $\mathcal{S.1}$ $\mathcal{SDL}_{xta}$ representation                                           |

| 6   | 5.2 The UPPAAL result                                                                          |

| 6   | Using the verifier in UPPAAL                                                                   |

| (   | Conclusion                                                                                     |

|     | 7.1 Related work                                                                               |

| •   | 7.2 Future work                                                                                |

|     | 7.3 Summary                                                                                    |

| '   | .o Summary                                                                                     |

| Ι   | Differences between SDL-92 and $\mathcal{SDL}_{xta}$                                           |

| Ε   | $BNF 	ext{ of } \mathcal{SDL}_{xta}$                                                           |

| Ε   | B.1 BNF                                                                                        |

| Ε   | 3.2 Global                                                                                     |

| Ε   | 3.3 Signal definition                                                                          |

| Ε   | 3.4 Communication syntax                                                                       |

| Ε   | 3.5 Referenced structures                                                                      |

| Ε   | 3.6 System definition                                                                          |

| Ε   | 3.7 Block and block type definition                                                            |

| Ε   | 3.8 Substructure                                                                               |

| Ε   | 3.9 Process and process types                                                                  |

| Ε   | 3.10 Declarations in process                                                                   |

|     | 3.11 States, Inputs and Queue interaction                                                      |

|     | 3.12 Transition                                                                                |

|     | 3.13 Label                                                                                     |

|     | 3.14 Output                                                                                    |

|     | 3.15 Task                                                                                      |

|     | B.16 Create and stop                                                                           |

|     | B.17 Decision                                                                                  |

|     |                                                                                                |

|     | 3.18 Set/reset of timers                                                                       |

|     | B.19 Nextstate                                                                                 |

| 1   | 3.20 Join                                                                                      |

| · F | Rules related to UPPAAL used in $\mathcal{SDL}_{xta}$                                          |

| . т | Usage of the conversion program                                                                |

| ${f E}$      | The   | signal analysis algorithm                                                | 80 |

|--------------|-------|--------------------------------------------------------------------------|----|

|              | E.1   | Output in a process set                                                  | 80 |

|              | E.2   | Out from process in a leaf block                                         | 80 |

|              | E.3   | Out from block in a system or a substructure                             | 81 |

|              | E.4   | Out of substructure in partitional block                                 | 81 |

|              | E.5   | Into a partitioned block                                                 | 81 |

|              | E.6   | Into a substructure                                                      | 82 |

|              | E.7   | Into a leaf block                                                        | 82 |

| $\mathbf{F}$ | The   | full $\mathcal{SDL}_{xta}	ext{-}\mathbf{code}$ for the exchanger example | 83 |

| $\mathbf{G}$ | The   | full Uppaal .xta-code for the exchanger example                          | 85 |

| Li           | ist o | of Figures                                                               |    |

|              | 1     | The path from SDL-92 to UPPAAL's .xta                                    | 7  |

|              | 2     | System behaviour of SDL                                                  | 11 |

|              | 3     | Process communication                                                    | 11 |

|              | 4     | System with block                                                        | 12 |

|              | 5     | Block with substructure                                                  | 13 |

|              | 6     | Block with process sets                                                  | 13 |

|              | 7     | Process, process type, block and block type                              | 15 |

|              | 8     | The SDL input symbol                                                     | 16 |

|              | 9     | The SDL save symbol                                                      | 17 |

|              | 10    | The SDL Task symbol                                                      | 18 |

|              | 11    | The SDL output symbol.                                                   | 19 |

|              | 12    | The SDL decision symbol                                                  | 19 |

|              | 13    | The SDL stop symbol                                                      | 20 |

|              | 14    | Textual description of sender receiver                                   | 22 |

|              | 15    | Simulation of UPPAAL text in Figure 14                                   | 23 |

|              | 16    | Possible, but not always                                                 | 25 |

|              | 17    | Impossible synchronization. $c$ cannot be in $[9,7]$                     | 26 |

|              | 18    | Generate of a process set                                                | 28 |

|              | 19    | Ta run-time system.                                                      | 29 |

|              | 20    | Ta signal paths                                                          | 32 |

|              | 21    | The $Expl$ ta process                                                    | 33 |

|              | 22    | An example PSO UPPAAL process                                            | 35 |

|              | 23    | The PSI Uppaal process                                                   | 35 |

|              | 24    | Principles of create.                                                    | 37 |

|              | 25    | An example $StartUp$ Uppaal process                                      | 38 |

|              | 26    | Start and stop principle. Excerpt from an sdlprocess                     | 39 |

|              | 27    | An example RemPid Uppaal process                                         | 40 |

|              | 28    | The Queue UPPAAL process generated for one parameter                     | 45 |

|              | 29    | Except of input in IJPPAAL                                               | 46 |

| 30 | Excerpt of input in SDL      | 46 |

|----|------------------------------|----|

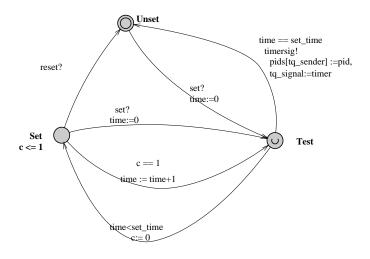

| 31 | The Timer Uppaal process.    | 55 |

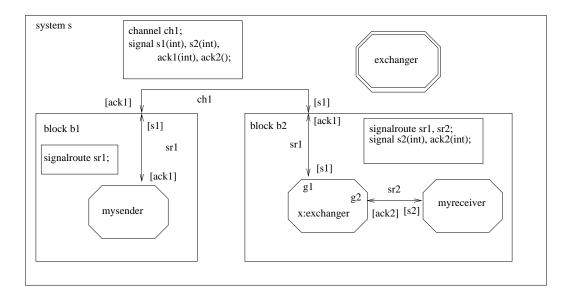

| 32 | The SDL system               | 57 |

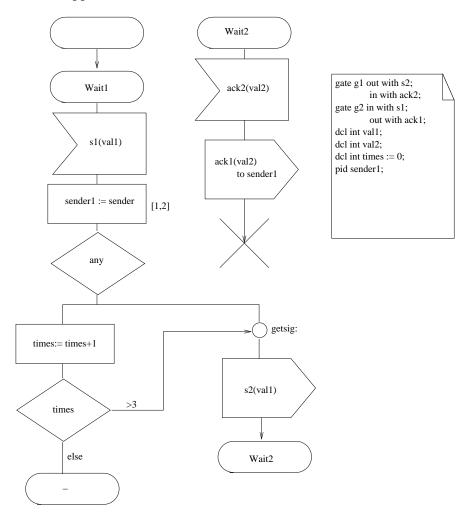

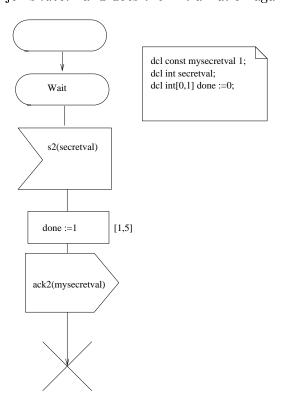

| 33 | The xchanger process type    | 58 |

| 34 | The SDL sender process       | 59 |

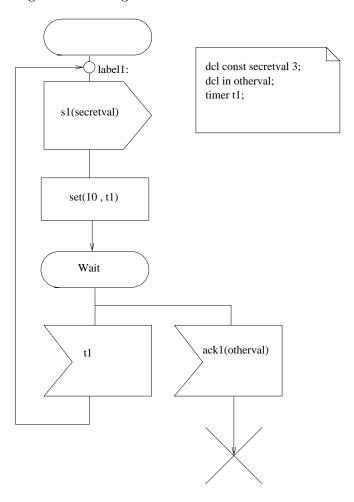

| 35 | The SDL receiver process     | 60 |

| 36 | The exchanger Uppaal process | 61 |

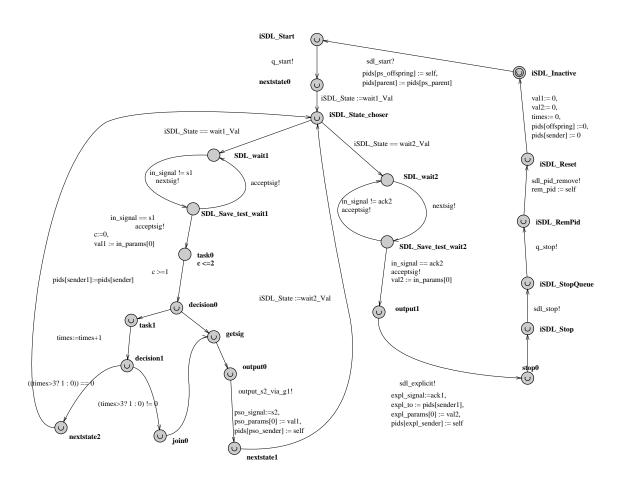

| 37 | The sender Uppaal process    | 62 |

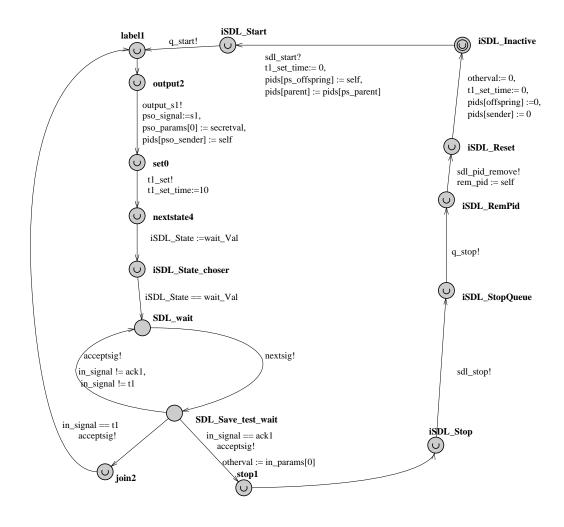

| 38 | The receiver Uppaal process  | 63 |

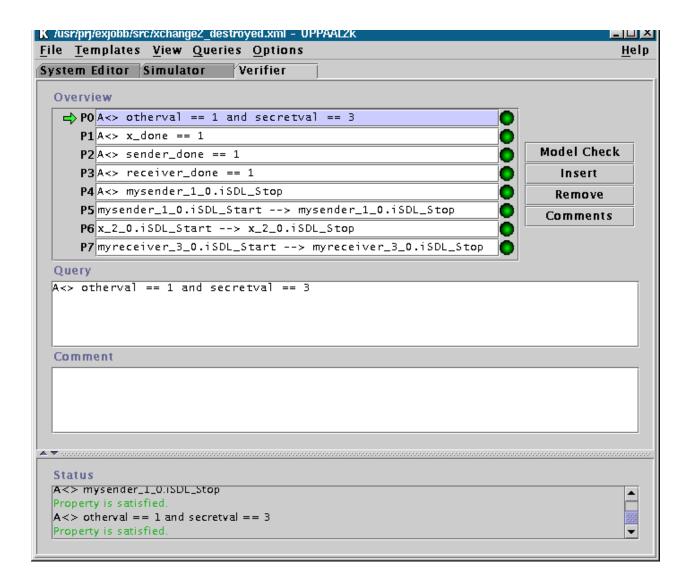

| 39 | The UPPAAL verifier          | 65 |

## 1 Introduction

## 1.1 Overview and objectives

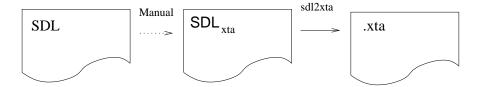

The objectives of this work is to describe, and implement, a translation from an SDL [Z.100] syntax to a language (xta) for the UPPAAL [LPY97] tool.

SDL is intended for the specification of complex, event-driven, real-time, and interactive applications involving many concurrent activities that communicate using discrete signals.

Although SDL is widely used in the telecommunications field, it is also now being applied to a diverse number of other areas ranging over aircraft, train control, medical and packaging systems [SDL02].

Although the behaviour of an SDL system is clearly defined by the semantics of SDL, analysis of the real-time behaviour is still hard to do for such a system. Timing is of paramount significance for correct behaviour. One of the problems is that the arrival order of signals to a queue matters for the behaviour. So, it would be very difficult to do an exhaustive testing on an SDL system during run-time. This is partially because we cannot control the order of arrival of signals to a process, at least not for signals internal to the SDL system. No matter how many times we test/simulate, it is possible that they always come in the same order at a specific state of the system.

Happily, there are verification tools for analysis of models of real-time systems e.g., UPPAAL. The basis of the UPPAAL model is the notion of timed automata [AD94] developed by Alur and Dill as an extension of classical finite-state automata with clock variables. If we could transform an SDL system into a network of timed automaton while preserving its behaviour we would be able to let UPPAAL do the verification.

The language used in our study is a variant of a subset of SDL. To separate SDL from our language we call our language  $\mathcal{SDL}_{xta}$ , (see Appendix B and C for the definition). The syntax of  $\mathcal{SDL}_{xta}$  is based on SDL version 1992 (SDL-92). It includes most of the features from SDL-88, but the data types are taken from UPPAAL's .xta format. We have also added a syntax for adding best and worst case execution time (BCET/WCET) for each action in an SDL process. We give an overview of the differences in Appendix A, Differences between SDL-92 and  $SDL_{xta}$ .

Figure 1: The path from SDL-92 to UPPAAL's .xta

#### 1.2 Conversion problems

There are several problems that we have to solve or work around. Data types in SDL are of less interest and we don't include them in our language,  $\mathcal{SDL}_{xta}$ . Examples of problems

we deal with in the  $\mathcal{SDL}_{xta}$  language are simulations of: implicit and explicit channels, queues, timers, dynamic process creation and process execution. Apart from timers we can also simulate worst and best execution time per action statement in the process.

In SDL, it is possible to specify systems at many nested levels of abstraction. At the other hand, in UPPAAL, models are flat, i.e., there is no hierarchy other than the process level and the global level. So, apart from the local variables we had to flatten every context in  $\mathcal{SDL}_{xta}$ .

In  $\mathcal{SDL}_{xta}$  a block or process can be specified as a type. That type can be used many times in its scope. Type instantiation has been one of the harder problems so solve, even if this matter is not specific to conversion into UPPAAL.

$SDL_{xta}$  uses asynchronous signals that are queued at input to the receiving process. This is very different from the way timed automata work. When two timed automata synchronize, they simultaneously make a transition (rendez-vous). In SDL, when a process sends a message there is no guarantee that the receiving process is ready to receive that signal.

We have had a difficult task to implement the behaviour of the SDL queue, because it has a complex behaviour. A process can save a set of signals when it is in a specific state. Signals that are not in the save set and for which there are no transitions, are discarded.

When an SDL process sends out a signal without specifying the destination by process id, then the destination is determined by combining several hints in the output in conjunction with the system structure specification. The problem of signal delivery is solved in the conversion, and it may result in more than one receiving process for an output. This is called implict signal addressing and is one of the major problems for which we propose a solution in this report.

We also attack the problem of dynamic creation of processes. We cannot allow an unbounded number of processes but we can simulate dynamic creation up to a maximum. One problem that arises from this is that the process identity numbering makes the search space for UPPAAL infinite.

We have to interpret all flow control in the process including, the state machine itself, decisions and joins in the transitions.

We simulate a system where all processes are concurrent. We do not take in account whether two processes runs in the same block or not. In our model we don't have any delay on signal delivery at all. The only time that we take in account is the processes' timers, and the best/worst execution time of actions, when such time is supplied by the user.

As UPPAAL cannot compare a clock value with a variable, we have done our timers so they count discrete time units and thereby we can make a delay until a certain amount of time has passed.

#### 1.3 Organization

The remainder of the document is organized in the following way:

- In Section 2, SDL, we give an introduction to SDL

- In Section 3, UPPAAL, we give an introduction to UPPAAL.

- In Section 4, SDL run-time system building, we present the architecture of, and the abstract ideas behind, the UPPAAL .xta code, that we generate. We also discuss signal analysis.

- In Section 5, *Process conversion*, we present the conversion of an SDL process. The communication between the queue and the process is explained. We also explain each SDL process action transition construct.

- In Section 6, Brief example, we give a first example.

- In Section 7, Conclusion, we discuss our achievements.

- In Appendix A, Differences between SDL-92 and  $SDL_{xta}$ , we give an overview of the differences between SDL-92 and  $SDL_{xta}$ .

- In Appendix B, BNF of  $SDL_{xta}$ , we present a Backus Nauer Form (BNF) for  $SDL_{xta}$  except the UPPAAL .xta part.

- In Appendix C, Rules related to UPPAAL used in  $SDL_{xta}$ , we present a Backus Nauer Form (BNF) the UPPAAL .xta part in  $SDL_{xta}$ .

- In Appendix D, *Usage of the conversion program*, we describe how to download and use the conversion program, sdl2xta described in this document.

- In Appendix E, *The signal analysis algorithm*, we outline the algorithm how possible receivers for an SDL output is found.

## 2 SDL

#### 2.1 Definition

Specification and description language (SDL)<sup>1</sup> is an object-oriented, formal language defined by The International Telecommunications Union Telecommunications Standardization Sector (ITU-T) (formerly Comitè Consultatif International Telegraphique et Telephonique [CCITT]) as recommendation Z.100 [Z.100]. The language is intended for the specification of complex, event-driven, real-time, and interactive applications involving many concurrent activities that communicate using discrete signals.

## 2.2 History

The development of SDL started in 1972. A 15-member study group within CCITT representing several countries and large telecom companies like Bellcore, Ericsson, and Motorola began research on a standard specification language for the telecommunications industry. The first version of the language was issued in 1976, followed by new versions in 1980, 1984, 1988, 1992, and 1996. The latest versions expanded the language considerably specifically the object oriented additions. Today SDL faces an itegration with OMG's *Unified Modeling Language* (UML) [SDL02].

#### 2.3 Behaviour overview

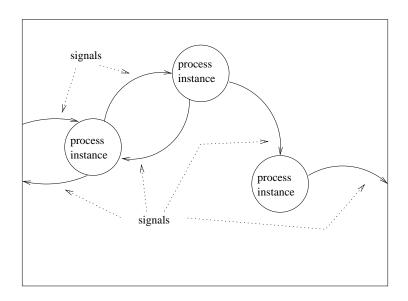

An SDL system is defined by the behaviour of the processes it consists of and how they are interconnected. By ignoring many details we can describe a SDL system at run-time as **process** instances that communicate by sending **signals** to each other and/or to the environment (see Figure 2).

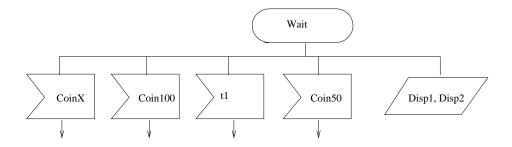

Each process can be viewed as a finite state machine [Holtz91] [Brau84], acting on input. Depending on its next input, the process performs a transition, that may include many actions, and finally moves to a new (possibly the same) state. Its next state may be determined by decisions in the actions. In SDL, a state is a location where only input from the queue can trigger a transition.

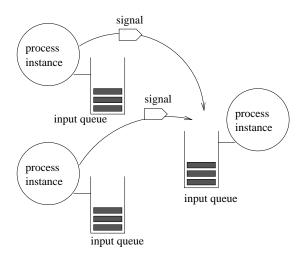

Communication in an SDL system is asynchronous. Figure 3 shows how transmitted signals are put in the queue of the receiving process instance. In Section 5.3 we will take a closer look at how a process instance interacts with its queue.

<sup>&</sup>lt;sup>1</sup>Proposals have been made to re-assign the acronym to System Design Languages [LNCS2078]

Figure 2: System behaviour of SDL.

Figure 3: Process communication.

#### 2.4 Structure

Structure is essential in SDL. At the top of the hierarchy of an SDL specification there is a system. A system contains blocks, futher a block contains processes or it could also be subdivided (or partitioned) into sub-blocks. We will call non partitioned blocks leaf-blocks. If a block is partitioned it contains only one substructure. A substructure contains blocks in the same manner as a system. We will not consider lower levels than the process level in this document.

We can thus identify the following hierarchical levels:

- $\bullet$  system

- partitioned block

- . . .

- partitioned block

- leaf-block

- process

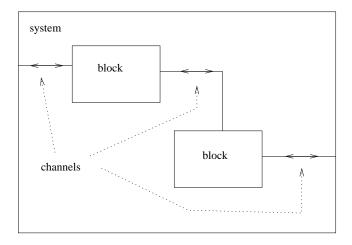

**System level** A **system** is the highest level building block in the hierarchy. A system consists of blocks connected by **channels**, a block can also be connected with the environment, see Figure 4. As the system is the higest level, connecting to the environment means connecting to an environment outside the specification. This could be I/O from a human user as well as from another system. When connecting to the environment, the system is considered as open. In  $\mathcal{SDL}_{xta}$  we will not allow an open system. In Section ?? we will address this issue more. A BNF for **system** in  $\mathcal{SDL}_{xta}$  is defined in Section B.6.

Figure 4: System with block.

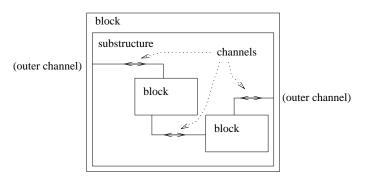

Partitioned block level A partitioned block is a block containing a block substructure that itself contains blocks, just like a system. A partitioned block is shown in Figure 5. In a block substructure, channels can connect two blocks or connect a block to an external channel. In a block substructure, an internal channel, with one endpoint connected to the environment, can be connected to one external channel. The  $\mathcal{SDL}_{xta}$  block substructure is defined in Section B.8.

Figure 5: Block with substructure.

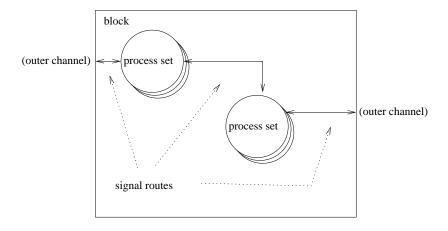

**Leaf-block level** In Figure 6, we show a **block** at leaf level. We will refer to this type of block as a leaf-block because is it a leaf in a hierarchy. A leaf-block contains processes. A process can be declared to have multiple instances. Therefore we refer to each process declaration as a process set. The communication channels in a leaf-block are called **signal routes**. A signal route can go from one process set to another process set or from a process set to the environment. A signal route that goes to the environment in a leaf-block is connected with a channel at the outside of the block. A BNF for **block** in  $\mathcal{SDL}_{xta}$  is defined in Section B.7.

Figure 6: Block with process sets.

**Process level** The dynamic behaviour of an SDL system is due to **process**es. A BNF for **process** in  $SDL_{xta}$  is defined in Section B.9.

#### 2.5 Communication

Signals A signal can be declared in a system, a block, a substructure or a process. A signal must be declared in the highest of the scopes that uses it. A signal can have parameters. A BNF for signal in  $\mathcal{SDL}_{xta}$  is defined in Section B.3.

Channels are used in systems and substructures. A channel has two endpoints, these endpoints can either be connected to blocks or to the **env**ironment. A channel can be uni-directed or bi-directed. The **with** construct restricts, for each direction, the set of signals the channel can convey. The **via** construct refers to a **gate**, which will be discussed in Section 2.6. Channels are delayed non-deterministically. This means that when a signal is sent through a channel there is no guarantee when it is delivered to the receiver, but as the channels are FIFO all sub-sequent signals must also be delayed until the first one is delivered. Since SDL-92, it is possible to use **nodelay** to declare a non delaying channel. In our study all channels are treated as if they were declared as non delaying channels. A BNF for **channel** in  $\mathcal{SDL}_{xta}$  is defined in Section B.4.

Signal routes Inside a leaf-block the communication channels are called signal routes. Signal routes are similar to channels. The with and the via constructs work in the same way as for channels. Signal routes are never delayed. A BNF for signal routes in  $SDL_{xta}$  is defined in Section B.4.

**Connect** The **connect** construct is used to connect an inner and an outer communication channel path in a block or block substructure. In a leaf-block, the inner communication channel will be a signal route. A BNF for **connect** in  $\mathcal{SDL}_{xta}$  is defined in Section B.7.

## 2.6 Types, instance sets, gates and references

**Types** There is a distinction between instances (or set of instances) and types in SDL descriptions. It is possible to define **types** of processes and blocks<sup>2</sup>. Types are not connected (by channels or signal routes) to any instances; instead type definitions introduce gates. These are connection points on the typebased instances for channels and signal routes.

Instance sets One can declare an initial and maximal number of instances for a process. This is the reason why we wrote process set instead of process instance in Figure 6. The default is; initial one and maximal one. When more than one process instance is active there is an ambiguity which instance that will receive a signal, if the signal isn't addressed by process id (see Section 2.10). Process instances can be started (created) by other instances and they can stop themselves. It is also possible to declare a number of instances for a block. Blocks are static and the number of instances cannot change during run-time.

<sup>&</sup>lt;sup>2</sup>Not system in  $\mathcal{SDL}_{xta}$

Gates A gate is a connection point used instead of **connect** in typebased instances (blocks or processes). When using types, channels and signal routes adds a "**via** gatename" on an endpoint connecting a boarder of a typebased instance (-set). At a gate one can restrict the set of signals going into or out from the block (or process).

**References** System, block, block type, process and process type specifications can be **referenced** (see Appendix B.5). A referenced specification is a specification placed in the global area that shall be considered to be at the place of reference.

**Scoping rules** A process with the same name can be specified in different leaf-blocks without any naming conflict. When block types, process types and signals are defined they can only be used where they are defined or in a sublevel to that specification. This is like an ordinary programming language with static scoping, e.g., Pascal.

## 2.7 Graphical and texual representation

In the BNF (see Section B) we use only SDL's textual representation (SDL/PR). This is natural because  $\mathcal{SDL}_{xta}$  is based on the textual representation and it is  $\mathcal{SDL}_{xta}$  that the transformation program in our study uses. SDL also has a graphical representation (SDL/GR) which we not define formally here. We use it to illustrate structure and behaviour.

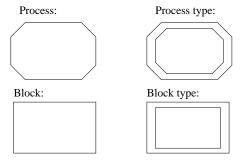

Figure 7 shows symbols for block, process and their types.

Figure 7: Process, process type, block and block type.

## 2.8 States and input behaviour of a process

SDL's process flowcharts are probably the most commonly known part of SDL. An SDL process can be thought of as a finite-state machine. It has a set of states and for each state it has a set of possible input signals. When one of the possible input signal arrives, the process moves from one state to another (possible the same) state. Such move is called a transition. A transition is a sequence of actions leading to another SDL-state. Transitions are described in Section 2.9. Signals can be saved in a state, that means; if a signal is

in the save-set of a state, then the signal can stay in the queue and other (later arrived) signals can be consumed. An arriving signal that is not in the save-set and has no transition specified for it, is discarded.

States In a state, the process waits for an incoming signal. The process queries the queue for the next signal and decides which transition it shall follow. A state is declared with the state keyword in a textual description. The initial state is an anonymous state declared with the start keyword in a textual description. In a state the inputs with their transitions and the save-set are declared. It is possible to specify some inputs for more than one state by emumerating the states that the inputs shall be connected to. The asterisk wildcard \* can be used following by a list of states inside parentheses indicating that the inputs for this "state" shall be considered as input for all states in the process except those inside the parentheses.

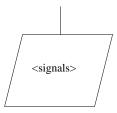

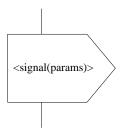

Input The graphical symbol of an input is shown in Figure 8. One or more signals can be in the input symbol, indicating that the following transition will be performed for any of the signals. Inputs are declared with the input keyword in a textual description. The asterisk wildcard \* can be used instead of specifying a signal or a list of signals. The asterisk means that for this state all signals except those declared at other inputs shall trig the performance of the transition that follows the input.

Figure 8: The SDL input symbol.

**Save** In a state a save-set can be declared that is saved as long as the process stays in the state. Save-sets are declared with the **save** keyword in a textual description. The graphical symbol for save is shown in Figure 9.

The asterisk wildcard \* can be used instead of specifying a signal set to save. The asterisk means that for this state all signals except those declared at other inputs are in the save-set.

Conditional and continuous input It is possible to declare an enabling condition on an input. Conditions are declared with the **provided** keyword in a textual description. If no signal is given for an input then the input is a *continuous* input. Such an input must be

Figure 9: The SDL save symbol.

guarded by a condition. A *continuous* input transition can be performed first when there are no other signals in the queue. The guarded input is not yet implemented in  $\mathcal{SDL}_{xta}$ .

**Priority** Signals with priority are treated differently in the input-queue. A signal with higher priority is sorted before other signals with lower priority (or no priority) in the input-queue. To set priority the **priority** keyword is used in a textual description. Priority 1 is higher than 2 etc. Priority is not implemented in  $\mathcal{SDL}_{xta}$ .

**Spontaneous transition** If the signal for an input have is named **none** then the succeeding transition is a spontaneous transition i.e., the succeeding transition can be activated without any stimuli for the process. This will make the state-machine non-deterministic. Spontaneous transitions are not implemented in  $\mathcal{SDL}_{xta}$ .

#### 2.9 Transition

Formally, a transition consists of a sequence of action statements with an optional transition terminator or just a transition terminator. Action statements and transition terminators will be explained in Section 2.10 and Section 2.11. If no terminator statement is given, then the process stays in the same state. The BNF of the transition, the action statement, and the terminator statement can be found in Appendix B.12.

Action statements As action statements we count tasks, outputs, decisions, set and reset of timers, and creation or processes. A task is used to do calculations, an output sends a signal to another process, a decision split the control into multiple paths depending on data, set and reset controls a timer, and create starts a new process instance.

**Terminator statements** As terminiator statements we count next state, join, and stop. Next state decides the process next state, join connects transfer the control to a particular place in another transition, and stop stops the execution of the current process instance.

## 2.10 Action statements

An action statement is an optional label followed by a task, an output, a decision, a set or reset of a timer, or a creation of a process. We will explan set and reset of timers in

Section 2.12 and creation of processes in Section 2.13.

**Label** A label marks a point in a transition where another transition can join by referring to the label name. A label is an identifier name followed by a colon.

**Task** In a task some computational work can be done, procedure<sup>3</sup> can be called, variables can be assigned etc. External actions can also be made here often expressed as informal text. Figure 10 shows the graphical symbol of a task.

Figure 10: The SDL Task symbol.

Output Communication between processes is done by sending messages. When a process sends a message it uses the action output. The keyword in the textual representation is output. In the textual representation the output construct consists of the output keyword, a signal identifier with optional parameters, an optional to construct, and an optional via construct.

The to construct consists of the keyword to followed by an identifier of the process to send to. The identifier could be a variable of type PId or a name of a process-set. The former includes the special SDL PId variables self, sender, parent, and offspring. Where self is the process' own pid, sender is the pid of the last handled signal, parent is the pid of the creator of the process, and offspring is the pid of the last created child created by the process. All except self variable can have value zero. The sender variable if the process hasn't received any signal, the parent if the process was created at initialization, and the offspring if no child has been created. The via construct consists of the keyword via followed by one or more identifiers. An identifier can be a gate, a signal route, or a channel. The purpose of the via is to show the path out from the process and thereby constrain the receiving process-sets. Figure 11 shows the graphical symbol of an output.

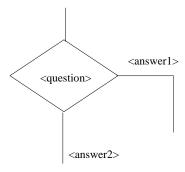

**Decision** A transition may split into two or more branches depending on some condition using the **decision** construct. The decision construct consists of a question and a decision body inside a **decision enddecision** pair. The decision body consists of answers, each of them has a continuing transition. One of the answers can be an **else** answer which is then the supplement of all other answers. After the **enddecision** all transitions that not

<sup>&</sup>lt;sup>3</sup>Procedures are not implemented in  $\mathcal{SDL}_{xta}$ .

Figure 11: The SDL output symbol.

end with a terminator statement are implicitly joined and continues with the consecutive transition. If the question of the transition is a any question, then all answers are empty and one of the answers is chosen randomly at execution. Figure 12 shows the graphical symbol of a decision.

Figure 12: The SDL decision symbol.

#### 2.11 Terminator statements

Nextstate, join, and stop are terminator statements. The stop statement will be described in Section 2.13.

**Nextstate** When a transition has been performed, then the control returns to a "stable" state, where the process waits for a new input signal. A nextstate construct consists of the **nextstate** keyword and an identifier for the next state. If an hyphen "-" is given instead of an identifier, control stays in the same state for the process.

**Join** Join has the same effect as a goto in a programming language. It directs the flow of control to a point that is marked by a label. This name is given in the join construct after the **join** keyword.

#### 2.12 Timers

A timer is declared (defined) inside a process. At run-time each process instance has its own set of the declared timers. A timer is set to expire at a certain time in the future. When a timer expires, it send a signal (named after the timer) to its process' queue. It becomes active when it is set and becomes inactive when it is reset or when its signal is consumed by the process. The timer's signal is put on its process' queue like all other signals, so it is possible for the process to set or reset the timer after a timer signal has been put on the queue, but before it has been consumed. In this case the timer signal is removed from the queue. This makes it impossible for the process to get the timer signal twice from the single set occasion or to get a timer signal after it has reset the timer.

**Set** The set statement consist of the **set** keyword and two arguments inside parentheses. In the first argument is a time expression and the second the name of the timer. The time expression is calculated in run-time to the time when the timer shall expire and send its timer signal. It usually contains an offset to **now**. The first argument can be omitted. In that case the timer expires at time "**now** + duration" where duration is derived from the timer definition.

**Reset** The reset statement consist of the **reset** keyword and inside parentheses the timer to be reset. After a timer is reset it cannot expire until it has been set again.

## 2.13 Process management

Create A create is used to spawn a new process instance of a process set. The create construct consists of the **create** keyword followed by the name of the process set wherein the new instance shall be made. After a process instance has been created the parent process gets the process id of its child process in a predefined variable named **offspring**. At startup, the child process gets its creators process id in the variable **parent**.

**Stop** When a process instace has done its work it can terminate itself with the stop statement. The **stop** keyword is used for this purpose. Figure 13 shows the graphical symbol of a stop statement.

Figure 13: The SDL stop symbol.

## 3 Uppaal

## 3.1 History

UPPAAL is an integrated tool environment for modeling, simulation and verification of real-time systems, developed jointly by Basic Research in Computer Science at Aalborg University in Denmark and the Department of Computer Systems (DoCS) at Uppsala University in Sweden. UPPAAL's first release was in 1995, and it has been applied in a number of case studies.

#### 3.2 Definition

UPPAAL consists of three main parts: a description language, a simulator and a model-checker. The description language is a non-deterministic guarded command language with simple data types (e.g. bounded integers, arrays, etc.). It serves as a modeling or design language to describe system behavior as networks of automata extended with clock and data variables. The simulator is a validation tool which enables examination of possible dynamic executions of a system during early design (or modeling) stages and thus provides an inexpensive mean of fault detection prior to verification by the model-checker which covers the exhaustive dynamic behavior of the system. The model-checker can check invariant and reachability properties by exploring the state-space of a system, i.e., reachability analysis in terms of symbolic states represented by constraints.

## 3.3 Modeling in Uppaal

When we take a closer look at the modeling language it is important to remember that the model is not executed but rather searched by the simulator or the model-checker. In the simulator we choose one of the possible transitions. All clocks in UPPAAL have fictive simulated time which has nothing to do with the wall clock or any other time counting unit. We will come back to this discussion later.

```

// Global declarations

int mytransferval := 0;

urgent chan mychan;

// Templates

process Receiver(urgent chan schan; int stransfer)

// local declarations

int secretval;

clock c;

// definition of locations

state begin, wait{c<=2}, end;

// definition of urgent locations

urgent begin;

// The initial location

init begin;

// Transitions

trans begin -> wait {

assign c := 0;

},

wait -> end {

guard c>=1;

sync schan?;

assign secretval := stransfer, stransfer := 0;

};

}

process Sender(urgent chan schan; int stransfer)

const secretval 3;

state begin, end;

urgent begin;

init begin;

trans begin -> end {

sync schan!;

assign stransfer := secretval;

};

// Process assignments (instantiation of templates)

mysender := Sender(mychan, mytransferval);

myreceiver := Receiver(mychan, mytransferval);

// System definition

system mysender, myreceiver;

```

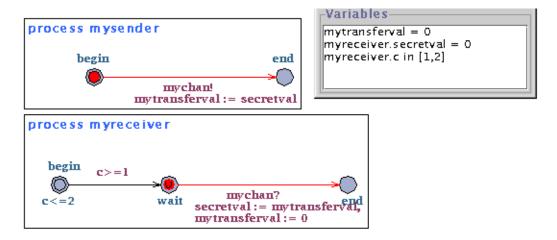

Figure 14: Textual description of sender receiver.

#### 3.4 Basics

An UPPAAL system is a collection of automata communicating with channels for synchronization and variables for sharing values. Each automaton has control nodes and transition edges describing its behaviour. The system's current state is defined by the processes locations, the variable and the clock values.

Figure 15: Simulation of UPPAAL text in Figure 14.

**System, Templates and Processes.** In UPPAAL's .ta format a system is declared with the keyword **system** follwed by the names of the processes included in the system. Global variables used in processes must be referred to directly. There is a one-one correspondence between a declared process and an instance in the system.

In the newer .xta format not processes but templates are defined e.g., *Receiver* in Figure 14, still the keyword **process** is used. A template is a process type with zero or more parameters. A process (as in the .ta format) is instantiated by parameterizing a templete. In simulation/verification time the .xta format will have been translated into the older .ta format. The result is shown in Figure 15. Therefore any reference to Figure 14 is also a reference to Figure 15.

**Locations.** Locations are the control nodes of an UPPAAL process. In Figure 14, the *Receiver* template has control nodes {begin, wait, end}. After the **state** keyword all the process states are listed. The begin location is the Receiver's initial location defined with the keyword **init**.

**Transitions.** A transition is an edge between two control nodes (locations) in an UPPAAL process. A transition may be guarded by a timing or data constraint, it may require a synchronization with another process and it may include a clock or data assignment. After

the **trans** keyword the transitions are listed for the process. A transition goes from one location to another e.g., wait to end in Figure 14.

**Guards.** Guards express conditions on the values of clocks and integer variables that must be satisfied for the transition to be taken. The keyword for guards in a transition is **guard** e.g., **guard**  $c \ge 2$ ; in Figure 14. See Section C for syntax on integer guards.

**Synchronization.** Synchronization means that two UPPAAL processes change location in one simulation step. Synchronization is done with (or via) channels. Channels are declared with the **chan** keyword e.g. *mychan* in Figure 14. To synchronize two processes a channel is specified after the **sync** keyword followed by a "!" for one of them and a "?" for the other, e.g. process mysender at location begin has a transition to location end with **sync** mychan! and process myreceiver at location wait has a transition to location end with **sync** mychan? Figure 14 shows templates that will be translated to this.

Assignments. Assignments can be done to integer and clock variables in transitions. An assignment is declared with the keyword assign. Clock variables can, in the current implementation, only be assigned with constant values. For an exact definition of assignments on integer variables see Section C. After the assign keyword a comma separated list of assignments is given, mixing assignments for integer and clock variables is no problem. In Figure 14 the mysender will communicate its secretval to myreceiver by assigning the global variable mytransferval, locally called stransfer in both mysender and myreceiver.

UPPAAL processes can communicate in two ways: by sharing data and by synchronization. Globally declared data is readable and writable for all processes, e.g. mytransferval in Figure 14.

## 3.5 Enforcing progress in the system

Without considering timing an automaton has the possibility to wait forever in a control location. Happily timed automata provide a number of ways to prevent this from happening.

- Invariants

- Urgent Locations

- Committed Locations

- Urgent Channels

Invariants. An invariant is a constraint on the clock values in a location. This put constraints on the simulator and the model checker. Consider Figure 14, where the *Receiver* has an invariant  $\{c <= 2\}$  on its wait location. The meaning of this is: The automaton can remain in location wait only as long as  $\{c <= 2\}$ . The transition from the wait location to the end location can only be taken when 1 <= c <= 2, expressed as "c in [1, 2]". This is shown in Figure 15.

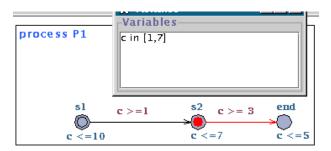

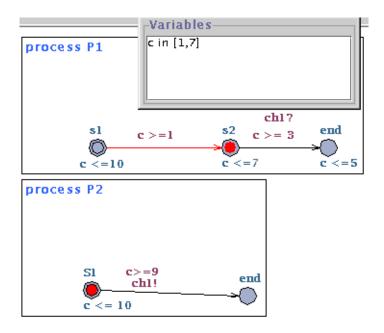

Figure 16: Possible, but not always.

In Figure 16 we can study how timing constraints work. The control is at location s2. When leaving location s1 we know by now that we have "c in [1,10]". When we enter location s2 we have "c in [1,7]" this is because of the invariant  $\{c <= 7\}$  on the location s2. Are we turning time backwards? No, the simulator observes that this transition is valid only when we have "c in [1,7]". Cases where "c in [7,10]" (that is 7 < c <= 10), are no longer valid after the step. But what if we have "c in [7,10]"? Don't we want to know about this potential model error? If we try to prove, with the UPPAAL's verifier, that we always can go from s1 to s2, then we will get a negative answer.

In Figure 17 we must have "c in [9,7]" because of the synchronization between the two processes P1 and P2. Though this is an impossible step the simulator will tell us that we have reached a deadlock.

Figure 17: Impossible synchronization. c cannot be in [9, 7].

**Urgent Locations.** "Urgent locations" are locations that the control must leave without any delay, as if we had an invariant  $\{c \le 0\}$  on the location and "assign c:=0;" on all incoming edges. This forces the actual process to always make a transition without any delay. Urgent locations are listed after the keyword **urgent** e.g, the wait state in Figure 14.

Committed Locations. "Committed locations" are even more restricted than Urgent Locations. No other process is allowed to make any simulation steps without being synchronized with the committed one. Committed locations are listed after the keyword commit.

**Urgent Cannels.** When a channel is declared as an urgent channel, then synchronizations via that channel has priority over normal channels and the transition must be taken without delay.

## 4 SDL run-time system building

When writing an SDL description we model a specification where processes are described in terms of process types, process definitions in a hierarchy of a system and blocks. In order to simulate the description, we must then convert the SDL description to an instance domain, we must also design a run-time system which manages process instances and communication. The interpretation of structure and communication from the SDL description is handled by SDL's meta processes such as system, timer and input-queue. The discussion of converting the behaviour of an individual process such as input, output, decisions and queuing, will be deferred to Section 5.

In this section we will outline how UPPAAL automata can work in a structure to simulate an SDL run-time system. We will also look at our implementation of SDL's meta processes in UPPAAL. This includes our solutions for: timers, dynamic process creation, and signal delivery.

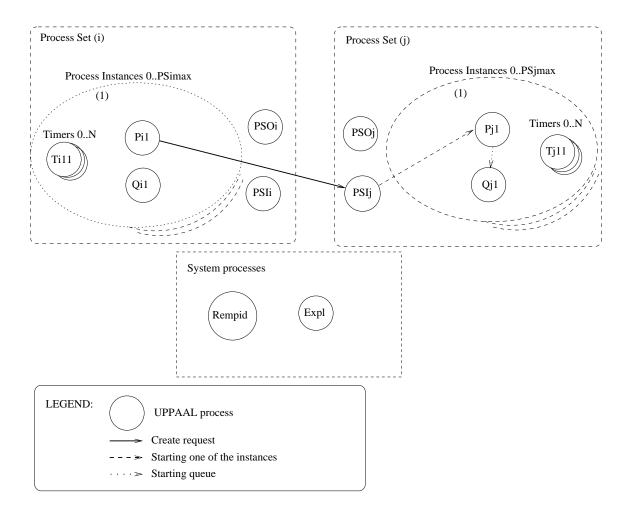

## 4.1 $\mathcal{SDL}_{xta}$ run-time overview

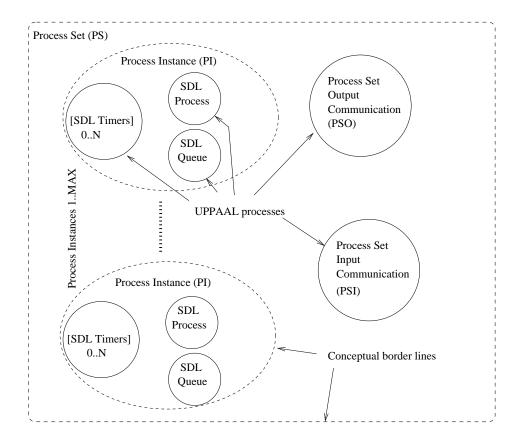

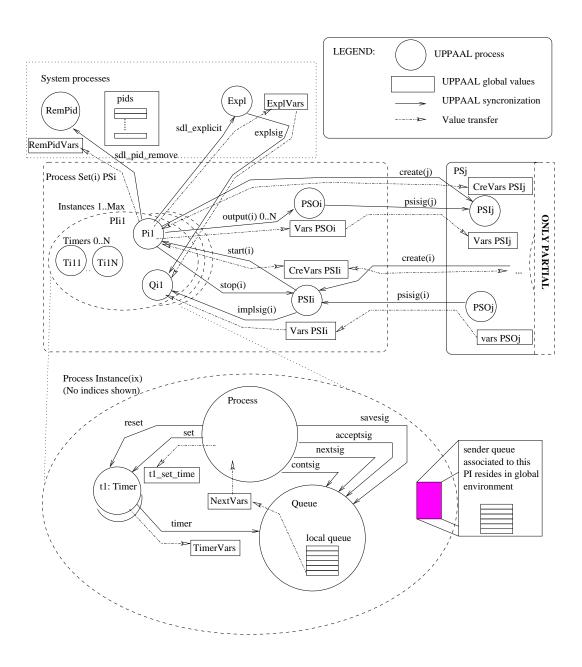

Each SDL process instance will have its own queue instance and a timer instance for each declared timer. Consider Figure 18, we have a dashed line, labeled  $Process\ Instance\ (PI)$  around the UPPAAL processes that are generated for each SDL process instance. We parameterizing UPPAAL templates in a appropriate way.

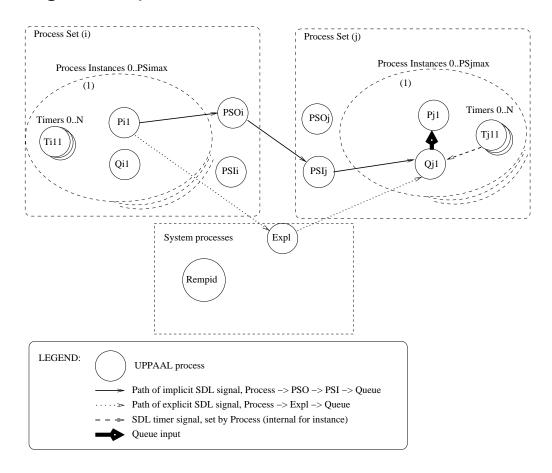

If we declare more than one instance of an SDL process, we get a process set. A process set is a collection of process instances, which differs only by their process id (pid). Signal routes that are connected to a process set are equally connected to all process instances. If an incoming signal is not addressed to a specific pid then each created process instance has equal opportunity to receive the signal. We simulate this signal ambiguity by means of an UPPAAL process called *process set input* (*PSI*), common for all instances in the process set.

When any process instance, in a process set, is sending a signal without specifying the receiving pid, then there can be more than one possible receiving PSI. This ambiguity is due to underspecification. To simulate this ambiguity we create, for each process set, an UPPAAL process called process set output PSO. In an SDL output it is possible to restrict the receiving PSIs by using SDL output's via or to construct. The task of the PSO is that for each output, it should route the signal to the right PSI. If there is more than one possible PSI then it shall chose one randomly. The PSO is shared by all process instances in a process set, just like the PSI. Figure 20 shows the UPPAAL processes that are involved at signal delivery.

When a signal has been sent and the receiving pid is specified the signal goes via a global UPPAAL process called Expl. When Expl receives a signal it send the signal to the queue with the specified pid. We will discuss this more thoroughly in Section 4.2.

In UPPAAL there are a fixed number of automata during the simulation/model check. To simulate dynamic creation and termination of processes we add locations where the automata are considered inactive. When an SDL process is about to create a new instance of another SDL process, it communicate with the PSI of the process set where the new

Figure 18: Generate of a process set.

instance is to be created. The PSI will, if there is any inactive instance left, activate one. In SDL we would get a new pid for each created process instance. This would make the search space for UPPAAL infinite and as a consequence make it impossible for UPPAAL's model checker to prove anything for all system states. Our solution is to reuse pids. An instance keep its pid even when it is inactive. By removing all knowledge of a pid in the system when the process instance terminating, we achieve an almost correct pid semantics. The work of removing a system's knowledge of a pid is done by an UPPAAL process called RemPid. Figure 24 shows the UPPAAL processes that are involved in process instance creation.

Figure 19: Ta run-time system.

In Figure 19 we show all types of processes, UPPAAL synchronizations, and data storage in our  $\mathcal{SDL}_{xta}$  run-time system. We henceforeward simplify the notation of the UPPAAL synchronization channels and variables by only using their functional names and thereby omitting the scoping prefix. The valid scope for each name is shown in Table 1 and Table 2. We give three examples to shed some light on this.

Firstly, when a process synchronizes over a nextsig channel only the queue in the same process instance can synchronize with it, i.e., a nextsig channel has a prefix so it is only "shared" inside a process instance.

Secondly, when a PSI synchronizes over a implsig channel any PI's queue process in the process set can synchronize with it, i.e., a implsig channel has a prefix so it is only shared inside its process set.

Thirdly, when the Expl (there is only one) synchronizes over the explsig channel any queue can synchronize with it, i.e., the explsig channel is globally known.

| Data storage globally shared |                  |                                              |  |  |

|------------------------------|------------------|----------------------------------------------|--|--|

| RemPidVars                   | rem_pid          | Pid for removal                              |  |  |

| Other global                 | qlive[]          | Bitarray for activation control              |  |  |

|                              | pids[]           | Storage for pids                             |  |  |

| ExplVars                     | expl_signal      | Signal                                       |  |  |

|                              | expl_params[]    | Parameters (array)                           |  |  |

|                              | expl_sender      | sender's pid. Index to pids[]                |  |  |

|                              | expl_to          | Destination pid, explicit addressing         |  |  |

| Data storage sl              | nared for a Prod | cess Set (PS)                                |  |  |

| Vars PSO                     | pso_signal       | Signal                                       |  |  |

|                              | pso_params[]     | Parameters (array)                           |  |  |

|                              | pso_sender       | Sender's pid. Index to pids []               |  |  |

| CreVars PSI                  | ps_offspring     | Index in pids[] to parents offspring         |  |  |

|                              | ps_parent        | Index in pids[] to parents pid               |  |  |

| Vars PSI                     | psi_signal       | Signal                                       |  |  |

|                              | psi_params[]     | Parameters (array)                           |  |  |

|                              | psi_sender       | Sender's pid. Index to pids []               |  |  |

| Data storage sl              | nared for a Prod | cess Instance (PI)                           |  |  |

| NextVars                     | in_signal        | Signal                                       |  |  |

|                              | in_param[]       | Parameters (array)                           |  |  |

| Other PI Vars                | self             | PI's pid, constant                           |  |  |

|                              | parent           | PI's creator's pid. Index to pids[]          |  |  |

|                              | offspring        | Last child's pid. Index to pids[]            |  |  |

|                              | sender           | Sender of last signal's pid. Index to pids[] |  |  |

| For each timer:t             | t_set_time       | Value timer $t$ is set to                    |  |  |

Table 1: Explanation of storage from Figure 19.

| Harrier shows to also the the showed               |                                                            |  |  |  |

|----------------------------------------------------|------------------------------------------------------------|--|--|--|

| UPPAAL channels globally shared                    |                                                            |  |  |  |

| sdl_pid_remove                                     | Syncs PI and RemPid when PI stops                          |  |  |  |

| sdl_explicit                                       | Syncs a sending PI and $Expl$ when explicit addressing     |  |  |  |

| explsig                                            | Syncs $Expl$ with the queue of the PI with the             |  |  |  |

|                                                    | right pid at explicit addressing                           |  |  |  |

| UPPAAL channels shared for a Process Set (PS)      |                                                            |  |  |  |

| output                                             | Syncs PI and PSO, one "output"-signal                      |  |  |  |

|                                                    | for every different SDL output implicit addressing         |  |  |  |

| psisig                                             | Syncs external PS's PSO with channel's PSI. Deliver signal |  |  |  |

| implsig                                            | Syncs PSI with PI's queue                                  |  |  |  |

| create                                             | Syncs external PS's $PSO$ PI with signal's $PSI$           |  |  |  |

| start                                              | Syncs <i>PSI</i> with PI, to start the PI                  |  |  |  |

| stop                                               | Syncs PI with $PSI$ , when PI stops                        |  |  |  |

| UPPAAL channels shared for a Process Instance (PI) |                                                            |  |  |  |

| savesig                                            | Process decide to save signal                              |  |  |  |

| acceptsig                                          | Process decide to save signal (or discard)                 |  |  |  |

| nextsig                                            | Process gets next signal from queue                        |  |  |  |

| contsig                                            | Process gets OK from queue to take the continous signal    |  |  |  |

| timer                                              | Syncs timer with queue                                     |  |  |  |

| set                                                | Process sets timer (one per timer)                         |  |  |  |

| reset                                              | Process resets timer (one per timer)                       |  |  |  |

Table 2: Principal UPPAAL channels in run-time system.

## 4.2 Signal delivery

Figure 20: Ta signal paths.

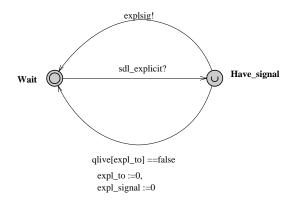

Explicit signal delivery For explicit delivery of signals the Expl UPPAAL process is used. There can be only one Expl process in the whole system. The Expl UPPAAL process is shown in figure 21. If an output action of a process explicitly sends a signal to a known pid, then there is a unique receiver. The sending process instance, synchronizes with the Expl process over UPPAAL channel sdl\_explicit which is globally known. In that synchronization, the process transfers data to unique global locations used by Expl, see ExplVars in Table 1. After this synchronization, Expl delivers the signal to the process instance with the destination pid. This synchronization uses the explsig UPPAAL channel. It is the input-queue of the process instance that receives and stores the data. There is a boolean value in a global array called qlive[] where the instances track if they are active or not. Instead of waiting for a process instance queue to synchronize, the Expl UPPAAL process discards the message if the receiving queue is inactive.

Figure 21: The Expl ta process.

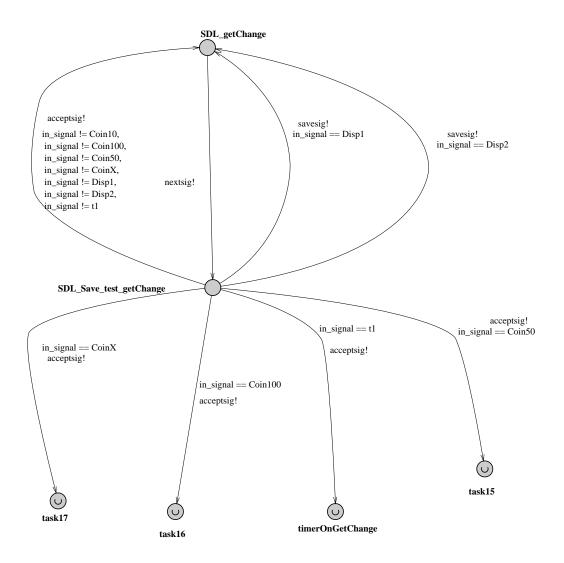

Implicit signal delivery When the pid for the receiving process instance is not known i.e., it is not given by the output action, the signal will take a different path to its destination queue. We will refer to such output as implicit signaling. Implicit outputs can be ambiguous. We have to simulate this ambiguity in the generated code. The signal analysis, described in Section 4.4 will for every output decide the possible process sets where the signal can be received. In a run-time system, this knowledge resides in the process set output (PSO) of the sending process instance.

An implicit output of an SDL-process is handled as follows. Firstly, the sending SDL-process synchronizes with its PSO process over an UPPAAL channel named after the signal and the contraints of the output. The PSO serves all process instances which shares this UPPAAL channel. In that synchronization the sending process instance transfers data to its PSO's storage called  $Vars\ PSO$ , described in Table 1. After this synchronization, the PSO synchronizes with one of the PSIs that is in the possible destination set. Here the sending PSO uses the receiving PSI's data storage,  $Vars\ PSI$ , the PSO and the PSO synchronize over PSI's UPPAAL channel for incoming signals. The PSI is unaware of which PSO it is communicating with. Lastly, the PSI transfers the signal to one of the process instances' queue. The PSI is serving the queues for all process instances in the process set, and when a signal is arriving via an implicit path, the receiving process instance is any of the (running) process instances. To get the desired effect we use ambiguous UPPAAL synchronization. That is, the PSI synchronizes with one of the queues. The queue reads the values from the  $Vars\ PSI$ .

To explain the functioning of the *PSO* consider Figure 22. We can see that its SDL-process has only one output, namely "output Money via sr1"<sup>4</sup>. There are two possible receivers of the signal, P1 and P2. The process set P1 has two instances. The latter observation comes from the edge that communicates with neither of the process sets. It is guarded with a test where all instances of all possible receiving process sets must be inactive for the transition to be taken. P1's instances are named P1\_1\_0 and P1\_1\_1. First we have the name of the process set (P1) then we add a unique number for this process set, in this case 1 and the last figure is an instance counter. For the process set P2 that has only one instance, that instance has the name of the process set.

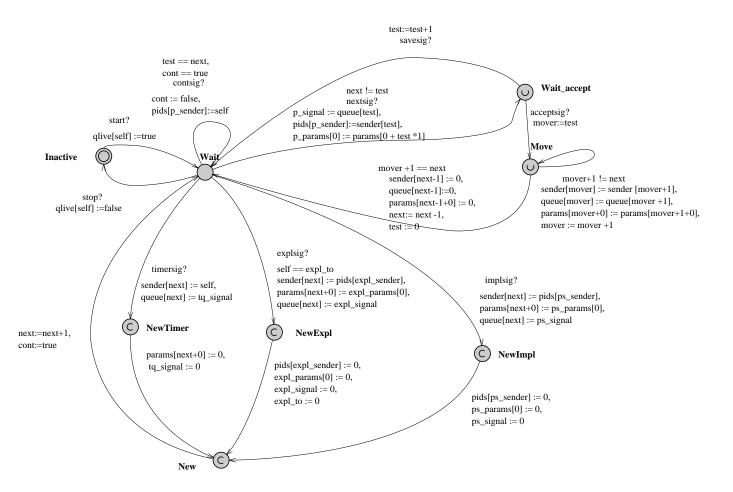

For the PSI consider Figure 23, it is a generic process. This UPPAAL template is used for all process sets. It is mediating the signals from a sending PSO to one of the input-queues in the PSI's process set. If there is no process instances started, it will not accept any signals. This forces the sending PSO to either send the signal to another PSI or discard it. The create and stop edges are part of the dynamical process management, described in the next section.

<sup>&</sup>lt;sup>4</sup>It can have more, if they are all exactly the same.

Figure 22: An example PSO UPPAAL process.

Figure 23: The PSI UPPAAL process.

## 4.3 Dynamic creation of processes

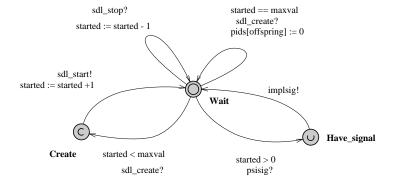

In this section we describe how we simulate dynamic creation of processes. In UPPAAL we can only use a fixed number of processes. This restricts us to a maximum of processes given at specification. A maximum number of instances can be specified for each process set, stating how many simultaneous instances a process set can have. When a process instance terminates, it gives room for a new instance, etc. Our solution is to generate the maximum number of instances and let them keep thier process id. SDL specifies that a newly created process instance shall have a new and unique process id. To follow this semantics and still keep the same process id we instead let the rest of the system forget about a process id when a process terminates. To get the right number of initial process instances per process set we create an UPPAAL process that starts the appropriate number of instances for each process set. Some instances are active and other are passive. We ensures that signals can be delivered only to an active instance's queue. We also have to make a control signal path from a creating process to the process set where an instance shall be created.

Process creation. When an SDL-process in a process set wants to start a process instance in another process set (or even its own), it synchronizes with the PSI of the process set it wants to start. Consider Figure 23. When the PSI gets a request for a creation of a new process instance and its maximum number of instances is not reached, it does a transition to the Create location. In this transition the creator has set the receiving process set's ps\_offspring value to a reference to its offspring value. Also it has set its own pid in the receiving process set's ps\_parent. Futher in the transition back from the Create location it commence execution of one of the process set's inactive instances. In that transition, the started SDL-process sets its pid to the creator's ps\_offspring and moves the ps\_parent to its own offspring.

Start the initial instances. The StartUp UPPAAL process has a very simple task. It creates the initial number of process instances for each process set. This is done in the same way as when a new process instance is created. For each process set where the number of instances at system start (the initial value) is greater than zero the StartUp UPPAAL process synchronizes with the PSI of the process set over the process set's create UPPAAL channel, once for each initial instance. Consider Figure 25; it creates on instance for the p1 process set and one for the p2 process set.

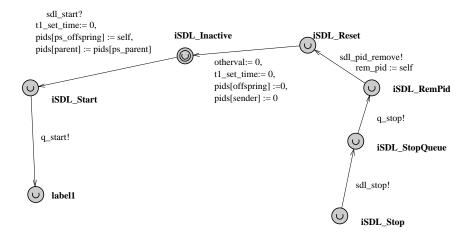

Start and stop of an SDL-process. In Figure 26 we show an excerpt of an UPPAAL SDL-process. At the location label1 the SDL-process starts and when it stops it goes to location iSDL\_stop. Note, we are using the iSDL\_prefix for internal SDL locations i.e., SDL process management. The locations shown are the start up sequence and the termination sequence. The initial state of the SDL-process is called iSDL\_Inactive. This location simulates that the process instance does not exist. When the PSI of the process instance gets a create message, the PSI synchronizes with a process instance over channel sdl\_start. The control moves to iSDL\_Start. In that move the creating and the created process instances exchanges pids. The ps\_offspring has been set to the index in pids[]

Figure 24: Principles of create.

where the creating process instance has its offspring and the *ps\_parent* index in pids[] has been set to the creating process instances' pid. In the move from **iSDL\_Inactive** to **iSDL\_Start** the created process sets the creators offspring (indirected) to its pid (self) and sets its parent (indirected) to the creators pid.

When moving from **iSDL\_Start** to the initiation actions the process instance's queue is started by a synchronization, locally called **q\_start**.

When an SDL-process stops it goes to the **iSDL\_Stop** location, starting a termination phase. When it moves from **iSDL\_Stop** to **iSDL\_StopQueue** it synchronize with its PSI. The PSI counts the number of active process instances and it can now decrease the number by one. When it moves from **iSDL\_StopQueue** to **iSDL\_RemPid** it synchronizes with its queue. After this synchronization the queue becomes inactive and can't receive any signals. When the control moves from **iSDL\_RemPid** to **iSDL\_Reset** it synchronizes with the RemPid process. In this move it also assigns the global rem\_pid variable, which

Figure 25: An example StartUp UPPAAL process.

decides on what pid the RemPid shall work. Last, when moving from **iSDL\_Reset** to **iSDL\_Inactive** we reset variables to the values that UPPAAL would have given them at system start up.

Figure 26: Start and stop principle. Excerpt from an sdlprocess.

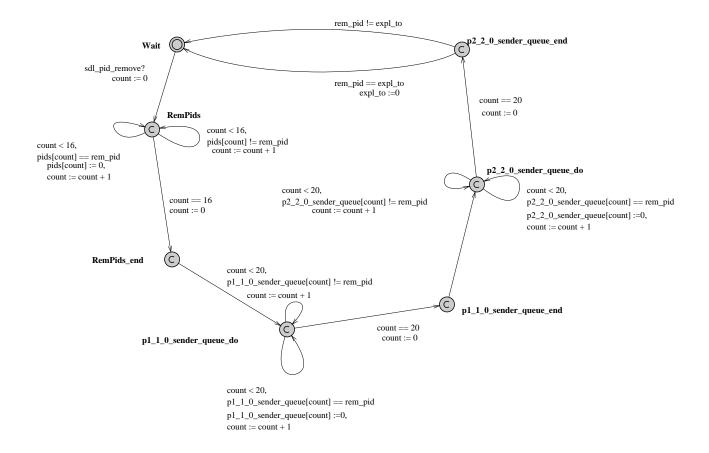

Pid removal. The RemPid UPPAAL process is a global process that is responsible for removing all references to a given pid. Every pid variable (local and global) that holds the pid value of a stopped instance has to be replaced with a zero. By doing this the pid is forgotten by the system outside the instance and can be reused if that instance is restarted. To make this work feasible for RemPid all pid values are stored in an array called pids[]. In the places where pids are used, instead of holding a pid we hold an index to the pid array where the pid value is stored. There are two exceptions to this rule, sender queues and the expl\_to. A sender queue is a queue of sender pids corresponding to a queue of signals that a Queue UPPAAL process holds. When a signal is sent that signal is associated with the pid of the sender. For every PI in the system there will be a sender queue that the RemPId has to go through.

Figure 27: An example RemPid UPPAAL process.

An example of the *RemPid* UPPAAL process is shown in figure 27. The *RemPid* starts in the **Wait** location. When an SDL-process synchronizes over the sdl\_pid\_remove channel it also gets the pid to remove in the rem\_pid data storage. In the **RemPids** location it exchanges all values equal to rem\_pid to zero in the pids[] array. When we have reached

the end of the array, in this case pids[16], we break and transit the control to a location called **RemPids\_end**. Futher, we do the same cleaning for the sender queues of the processes p1 and p2. Lastly, we clean the expl\_to value if necessary. All these stages are done using committed locations as to have no interruption while doing this cleanup.

### 4.4 Signal analysis

In this section we present the analysis of *implicit* signal paths. This analysis gives the information for the PSO to know the set of possible destination PSIs for each output action of an SDL-process. There are three parameters for each output: signal, via and to, where via and to are optional. If these parameters are exactly the same for two outputs, then they share the same set of possible destination PSIs. Our task is to follow signal routes and channels, with the constraints given by the parameters (signal, via, to) to get a set of PSIs.

The algorithm is basically to follow every signal route from the process set to the process set it is **connected** to, or to the **environment**, where we follow the channel(s)<sup>5</sup> that the signal route is connected to, or in the case where the block is typebased and the signal route is connected to a gate, we follow the channel(s) connected to that gate. When following a channel into a block we can also have more than one continuation. Absence of specification is treated liberally. This means that if no signal routes/channels are specified, then there are implicit signal routes/channels to all possible destination, in the block/system where signal routes/channels are omitted. There is still no possibility for a channel/signal route to go from the environment to the environment, which is forbidden in SDL. During the algorithm, we must respect the following constraints.

- The output's signal name must exist in every **with** clause of the passed gates, signal routes and channels for the direction in which the signal is traveling. If no with clause is specified then the signal is allowed to pass any signal route, channel or gate.

- The optional **via** constraint specifies a list of names which shall match with a name of a gate, a signal route or a channel, in the given order<sup>6</sup>. This is, when we encounter a situation where there are more than one possible continuation path and the first in the via list matches one of them, then we must use that and only that continuation. After this we have used the first via constraint which is then removed from the list for that continuation. If we reach a process set and the list isn't empty then that process set is not a possible receiver for the output.

- The optional **to** constraint specifies the name that a receiving process set must have. If we reach a process set that does not have the specified name then that process set is not a possible receiver for the output.

An outlined version how each level is searched is in Appendix E.

<sup>&</sup>lt;sup>5</sup>We allow multiple channels to be connected to multiple signal routes, this feature belongs to SDL-92.

<sup>&</sup>lt;sup>6</sup>At the time of writing, sdl2xta can only handle a single via name

### 5 Process conversion

In this section, a solution to the problem of converting an  $\mathcal{SDL}_{xta}$  process to an UPPAAL process, is presented. There are two distinct areas in an  $\mathcal{SDL}_{xta}$  process, namely the declaration area, and the process body.

#### 5.1 Process' declarations

A process' declarations consists of both definitions and declarations.

Gate definitions If the process defined as a type based process then it might include gate definitions. In that case all gate definitions must come before any other definition. There is no output generated that corresponds directly to gates. In the conversion program gates are used to restrict the possible receivers of output signals. This is done in the signal analysis.

**Signal definitions** Signals internal to the process can be defined. A signal defined inside a process (type) definition can not be sent to another process (not even if the receiving process has the same type). The number of parameter must be the same as when the signal is used. Each instance of a signal definition, generates a unique UPPAAL constant with the signal's name as identifier.